可编程逻辑器件

可编程逻辑器件(英语:Programmable Logic Device,缩写为PLD)是一种电子零件、电子组件,简而言之也是一种集成电路、晶片。PLD晶片属于数字类型的电路晶片,而非模拟或混合信号(同时具有数码电路与模拟电路)晶片。

PLD与一般数码晶片不同的是:PLD内部的数码电路可以在出厂后才规划决定,有些类型的PLD也允许在规划决定后再次进行变更、改变,而一般数码晶片在出厂前就已经决定其内部电路,无法在出厂后再次改变,事实上与一般的模拟晶片、混合信号晶片一样,在出厂后就无法再对其内部电路进行调修。

发明之前

在PLD还未被发明前,已有人将只读存储器(ROM)晶片以PLD的概念来运用,用ROM晶片来充当一些输入性的组合逻辑(combinatorial logic)函数。

首先一颗ROM晶片有m个输入(地址线,或称:地址总线、寻址线)以及n个输出(资料线,也称:资料总线,在此也可称:资料输出线),当ROM被当成存储器使用时,它就有个n bits的记忆存储空间。

输入部分不再是个m-bit的地址线路,而被看成是有m个相互无关连的独立逻辑信号线。且就理论而言一颗ROM晶片内可以放置个布尔(Boolean)函数,且每个布尔函数可以有m个逻辑信号。

但是这种用ROM“乔装”成的PLD,碍于ROM自身原有的结构设计,使真正有效的函数数取决于输出接脚(也称:脚位、引脚)数,因此有n个输出就只能有n个可用的有效函数。更简单的说,这时候的ROM等同于n组相互无关的独立逻辑电路,每组电路的产生、形成,则取决于由m个输入所组成的逻辑函数。

使用ROM来当PLD的好处是:有几个以m输入方式表示的逻辑函数,就会有几个对应的n输出,且绝大多数一般性用途的组合逻辑器件都可适用此种作法。同样的,PROM(Programmable ROM)、EPROM(ultraviolet-Erasable PROM)、EEPROM(Electrically Erasable PROM)等也都可以用此种方式进行逻辑规划、程序化,而且不需要特殊的软硬件,只要用标准的PROM刻录器即可实现程序化。然而,无论怎么说,这种作法也有些缺点:

- 与真正专精的逻辑电路相比,在反应速度表现上慢了太多。

- 在异步(也称:异步)的逻辑状态转变下,无法提供安全性的状态“防护,cover”。

- 过于耗电(同样是与真正专精的逻辑电路相比)。

- 整个ROM中仅有小部分的记忆存储空间能被有效使用,其余都形同浪费。

此法也不易于用于时序逻辑电路(sequential logic)中,因为ROM里头并不具备触发器(flip-flop,简称:FF)。

对电路设计的业余爱好者来说,有时也仍然用普遍型EPROM晶片来充当PLD,这种用法有时也称为“穷人的PAL”(PAL是PLD的一种)。

早期的可编程逻辑

|

主条目:可编程数组逻辑 |

第一个在商业化市场运用的PLD,是由Monolithic存储器公司(Monolithic Memories, Inc.,简称:MMI)所推出的可编程阵列逻辑(Programmable Array Logic,简称PAL)(此点有争议,详见讨论页),虽然IBM公司在1970年代中也有研制类似的装置(器件),但仅在该公司内部使用。

MMI公司在20-pin(20支接脚、引脚、脚位)的PAL方面相当成功,之后超微(AMD)公司也推出了22V10,22V10也是颗PAL,具有原先PAL所有的特性特点,但接脚数增至24-pin。更之后AMD公司收并了MMI公司(约1987年,待查证),并将其纳入自身的PLD部门,数年后AMD以百分之百转投资的方式将PLD部门分立成独立的威特信(Vantis)公司,到了1999年则由莱迪思半导体公司收购AMD公司手中的Vantis公司股份,自此收并Vantis公司。

GAL

以PAL(可编程数组逻辑)为基础的接续创新是通用数组逻辑(Generic Array Logic, GAL),此是由莱迪思半导体公司所发明,GAL的特性与PAL相同,不过PAL的电路配置、配置只能进行一次的程序刻录,不能再有第二次,而GAL则是可以反复对电路配置、配置进行刻录、清除、再刻录、再清除。

GAL这种可重复刻录的特性在研发过程时的试制阶段(prototyping stage)中特别好用,一旦在逻辑电路的设计上发现有任何程序错误,若是用GAL就能够以重新刻录的方式来修正错误。此外GAL也可以用PAL的刻录器来进行刻录及再刻录,虽然现在已经有可在线刻录(In-Circuit Programmable,有时也称:In-System Programmable)的ispGAL22V10。

另一个与GAL相类似的是PEEL(Programmable Electrically Erasable Logic),是由International CMOS Technology(简称:ICT)公司所提出。

CPLD

|

主条目:CPLD |

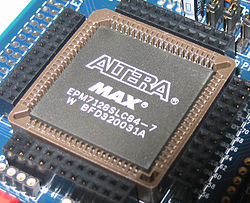

PAL、GAL仅适合用在约数百个逻辑门所构成的小型电路,若要实现更大的电路则适合用CPLD(Complex PLD,复杂型PLD),一颗CPLD内等于包含了数颗的PAL,各PAL(逻辑区块)间的互接连线也可以进行程序性的规划、刻录,CPLD运用这种多合一(All-In-One)的集成作法,使其一颗就能实现数千个逻辑门,甚至数十万个逻辑门才能构成的电路。

至于CPLD的程序刻录方式,虽然有些CPLD可以用PAL的刻录器来进行刻录,但这种刻录方式对经常有数百只接脚的CPLD来说并不方便。另一种刻录方式是CPLD已焊于印刷电路板上,之后透过额外的临时外接,或原有线路的内接,使CPLD与个人电脑间能获取连线,由个人电脑以串列或并行方式将新的刻录资料发送到CPLD上,而CPLD内部也具有解码电路能对接收到的资料进行还原解析,之后再进行重新的刻录,以此方式让CPLD内的程序(也可称:电路)获得更新。

要注意的是,每家业者的CPLD晶片多具有焊接后再行传输、再次刻录的技术,但各家的技术实现方式与名称多不尽相同,例如莱迪思半导体公司就将此种刻录技术称为“in-system programming”。

各家独创、专属的作法也逐渐消失,朝共通的标准、一致的方向发展,如IEEE 1532。

FPGA

|

主条目:现场可编程逻辑门阵列 |

当PAL忙于进展成GAL、CPLD时,另一种“可编程”的流派也逐渐成形,此称之为场式可编程闸数组(Field Programmable Gate Array,简称:FPGA)或现场可编程闸数组,FPGA是以闸数组(Gate Array)技术为基础所发展成的一种PLD。

FPGA早期的例子是Signetics公司在1970年代晚期所推出的82S100(数组)及82S105(测序器、编序器),其中82S100为“与,AND”型的闸数组,而82S105也相同,但再追加触发器(Flip Flop,cn处也称:触发器)的功能。

FPGA运用一种逻辑门式的网格(Grid),这种网格与普通的“闸数组”相类似,网格可以在FPGA晶片出厂后才进行配置配置的程序性规划。至于为何要称“场式可编程”就有些难懂了,“场式,Field”对晶片生产厂以外的世界来说是个工程方面的专业术语,然而厂外也是晶片买主的所在处。(言下之意是:不应当以这种艰涩难懂的工程用词来做为晶片产品的推行名称)

FPGA通常也可以在焊接后再进行程序刻录、变更的工作,此在某种程度与大型的CPLD相似。而绝大多数的FPGA,其内部的程序配置配置是属于易失性的,即是无持续电力供应后配置配置的内容就会消失,所以在装置(也指:器件、晶片)重新获得电力后,就必须将配置配置内容重新加载(re-load)到FPGA中,或者期望改变FPGA内的配置配置时,也必须进行重新加载的动作。

而关于配置配置的内容,就一般来说会存放在非易失性的存储器中,如PROM或EEPROM,若是用EEPROM,则或许也能用在线刻录(In-System Programmable,ISP)的方式来再次改变配置配置的内容(一般来说是透过JTAG接口来进行ISP)。

FPGA与CPLD都很适合用在特殊、特定的工作上,这是以此类晶片的技术本质来做为合适性的考量,然而有时在以经济性为主的权衡评估下也适合使用FPGA、CPLD,或者有时也会以工程师的个人偏好与经验来决定。

其他类型的PLD

除上述外,也有许多可再配置配置的系统(多指“晶片”)。例如:有些微处理器内除了一些固定性功效的电路外,其他部分的电路则可以依据微处理器所执行的代码而改变其功效。要想设计这种半变动式的系统,工程师需要学习新方法,甚至可能要用新的软件工具才能够开发。

另外,现在销售的PLD中,有的也会在晶片内提供一个具固定性功效的微处理器,然后微处理器的四周位置则设有许多可供配置配置的可编程逻辑(也因为处理器位在其中,所以也被称为核心),此种作法的好处是可以让设计者更专注在为他的设计增加新的功能特点,而少去担心“如何让微处理器运作”之类的基础性设计。

维持PLD的电路配置与配置

在一个PLD内有逻辑部分也有记忆部分,记忆部分是用来存储配置配置的程序内容,而存储的方式多是存放在可供PLD使用的集成电路(也称:集成电路)中,这包括:

- Silicon antifuses(硅反熔丝)

- SRAM(静态随机存储器)

- EPROM or EEPROM cells(EPROM或EEPROM的记忆晶格)

- Flash memory(闪存,也称:闪存)

硅反熔丝主要是用于PAL内,方式上是在PAL内部可编程的矩阵中,若期望矩阵中的某处、某一位置能够形成连接连线,则对该位置的行、列两端施压一个刻录烧写电压(此电压通常高于一般运作时的电压),如此该位置就会形成连接的短路、闭路(short)状态,相反的未施加电压的地方则保持开路(open)状态,由这开路、闭路来形成逻辑的0、1存储。不过一旦某位置被施加烧写电压而形成短路后,就无法在恢复成开路状态,但其他仍保持开路的位置,仍可施压电压使其短路,不过整体来说硅反熔丝仅适合一次性的配置配置刻录,一旦烧写的内容有错误,该颗PAL即宣布报废。此外,之所以称为“反熔丝”,理由是它的特性原理恰巧与一般日常所用的熔丝、保险丝相反,保险丝平时为短路,而被施加较高电压时便会烧断,成为永久性的断路、开路,反熔丝却是平常为断开,施加电压后反成为连接的短路、闭路。

SRAM属于易失性的存储器,这表示它在每次失去供电后就无法保存资料,若有PLD使用SRAM做为其配置配置的存储记忆(多数为FPGA),则每一次重新供电后就必须再次将配置配置资料加载(load,用意等同于将程序刻录烧写到PLD内)到PLD的SRAM中,不过此一送电后重新加载的程序,通常是交由另一部分的电路以自动化方式来执行,此一“开机后自动将程序加载到PLD内”的电路,过去是在PLD外部另行设计,但现在也有集成(也称:集成)到PLD内部的作法。

EPROM的记忆晶格是一种MOS(metal-oxide-semiconductor,金属氧化半导体)型的晶体管,若对该晶体管的栅极进行充电,则该充电后的状态就会成为一个记忆留存,之后无论晶片有无供电都可以持续维持着该状态,直到数年后充电状态才会消退消失,而透过对各记忆晶格的充电有无就能够存储0、1的配置配置。至于记忆资料当如何抹除(也称:拭除、擦除),这必须用强烈的紫外线对EPROM进行照射,以此强迫各栅极将原有的充电加以释放,且时间必须长达数十分钟才能全部抹除,否则会有抹除不完整的情形,此一抹除程序多是用所谓的“紫外线EPROM抹除盒”,英文称EPROM eraser,即是一个小盒子内设有紫外线灯管,之后将EPROM放入盒内,再将盒子的电源开启并点亮紫外线灯管,让紫外线照射EPROM,以此来进行清除,也因为紫外线对人体有害,所以才要在密闭不透光的小盒子内进行照射,此外为了方便工程师使用,抹除盒通常还设有定时装置,时间到后会自动提醒工程师已经达当初设置的照射时间。

闪存具有非易失性,即是断电后仍可保存记忆内容,且需要时它也随时能再清除抹除(erase)、再刻录烧写(program、reprogram)。

时至2005年,多数的CPLD都已使用电气方式烧写与电气方式抹除,并以非易失性方式来记忆。因为经过事实验证,在太小的逻辑运用中用SRAM来存储逻辑配置配置,则每次重新送电启动就必须再次进行加载烧写,如此实在过于麻烦,所以才会改成以非挥发方式来进行记忆存储。此外,若是用EPROM方式进行存储,且为了能够再次抹除与再次烧写,则PLD在其晶片封装上就必须使用陶瓷材质的封装,并在EPROM裸晶(Die)位置的上端设立石英材质的透光窗,好让紫外线能够照射入内,如此才能抹除EPROM裸晶上所存储的配置配置资料,而这种封装方式远贵于一般的塑胶材质封装。

PLD的编程语言

以手工的方式来产生JEDEC档过于复杂,所以多半改用计算机程序来产生,这种程序称为“逻辑编译器”(logic compiler),它与程序开发撰写时所用的软件编译器相类似,而要编译之前的原始代码也得用特定的编程语言来撰写,此称之为硬件描述语言(hardware description language, HDL)。

硬件描述语言并非仅有一种,如ABEL、AHDL、Confluence、CUPL、HDCaml、JHDL、Lava、Lola、MyHDL、PALASM、RHDL等,但目前最具知名也最普遍使用的是VHDL与Verilog HDL。

附注

- ^ - 就理论发展过程而言,在ROM类还历经了一小段PLA(Programmable Loigic Array)发展,之后才有PAL,ROM、PLA三者的主要差别是:ROM仅在输出的OR(或)数组可进行配置配置的规划,而PAL仅能在输入的AND(与)数组进行规划,而PLA两者皆可。

- ^ - 事实上除了可改写(Rewritable)外,GAL与PAL间的更大差别在于GAL的输出端追加了输出宏晶格(Ouput Logic Macrocell,简称:OLMC)的设计,使逻辑输出有更多的控制方式,使GAL比PAL更方便用在与时序逻辑电路的搭配上。(“巨集”也称为“宏”)

- ^ - 相对于“Field-Programmable,场刻录”一词的是“Mask-Programmable,遮罩、遮盖式刻录”,即是指用光掩模(Mask,也称:掩膜)方式曝光后刻蚀而成的电路,也就是ASIC的工艺方式,只能在晶圆厂使用的程序刻录法,更正确的说是:(积体、集成)电路的制造法。

外部链接

| |||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||

Text is available under the CC BY-SA 4.0 license; additional terms may apply.

Images, videos and audio are available under their respective licenses.